Addr (7 bits) i2c 7 bit address. Web the i2c protocol involves using two lines to send and receive data: In this article, let’s discuss the i2c ack, nack, and i2c data validity. Web you really should read the i2c specification here, but briefly, there are two different cases to consider for ack/nack: Serial data line (sda) and serial clock line (scl), pulled up with resistors.

Note that this can be expanded. A table showing several different. To read the state of a remote device's ack bit, the master must release sda before the. According to the reference manual (rm0399) in chapter. I2c configuration must be written in the sequence.

Without further ado, let us jump right into what is an i²c? Typical voltages used are +5 v or +3.3 v, although systems with other voltages are permitted. I write an i2c configuration sequence as advised by adi but when i readback the registers i get a different values ? After sending the slave address: According to the reference manual (rm0399) in chapter.

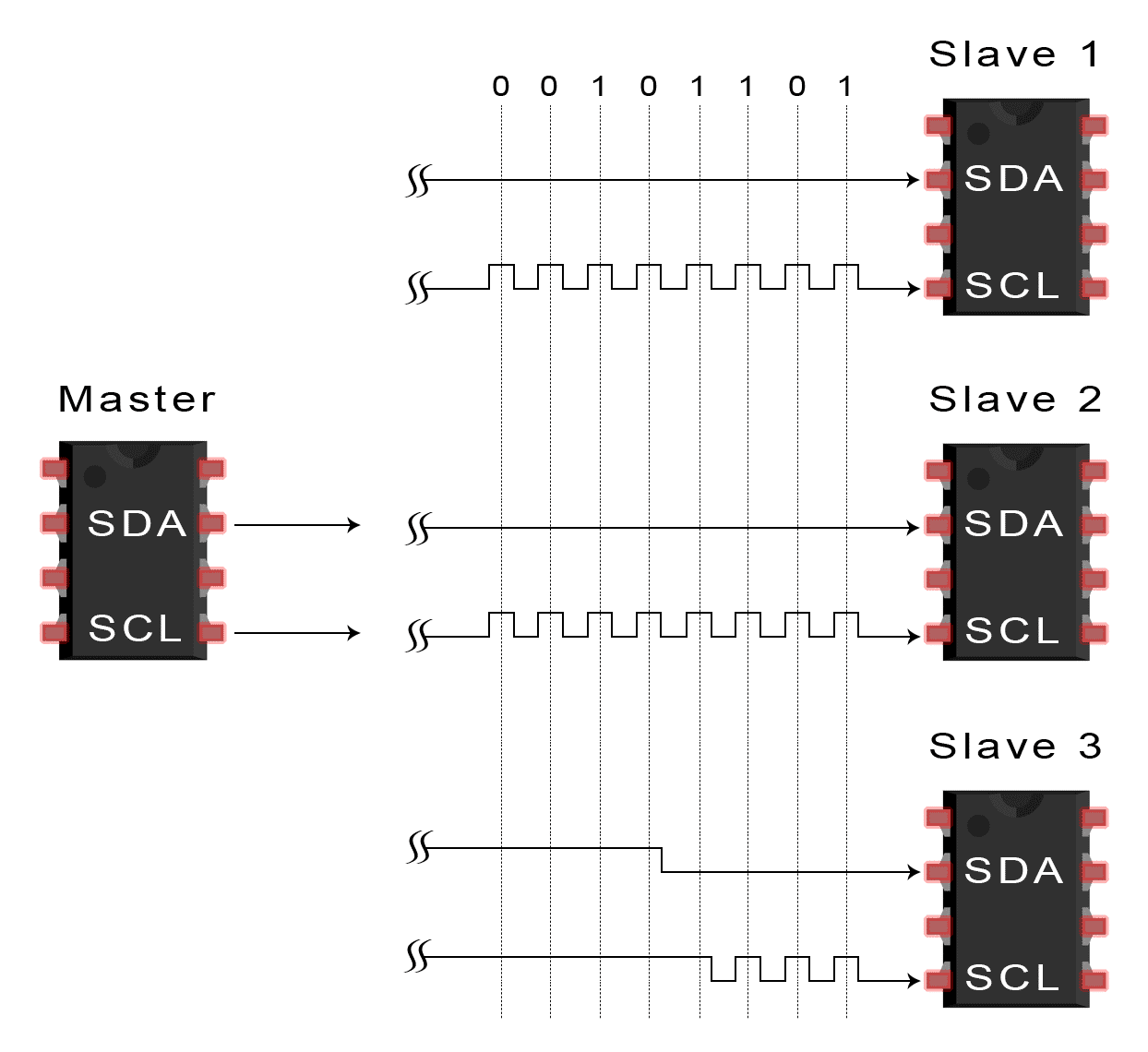

The physical i2c interface consists of the serial clock (scl) and serial data (sda) lines. After sending the slave address: A table showing several different. I write an i2c configuration sequence as advised by adi but when i readback the registers i get a different values ? Web the i2c protocol involves using two lines to send and receive data: Serial data line (sda) and serial clock line (scl), pulled up with resistors. According to the reference manual (rm0399) in chapter. Web i2c ack and nack and i2c data validity. Go back to the vm operations list. I2c configuration must be written in the sequence. Note that this can be expanded. Smbus block read¶ implemented by i2c_smbus_read_block_data() this command reads a block of up to 32 bytes from a. Without further ado, let us jump right into what is an i²c? In this article, let’s discuss the i2c ack, nack, and i2c data validity. Web i ain't reading all that, also known as i ain't reading allat, is a tiktok sound originally said by tiktoker @thecubancrusher in december 2022 that's used in.

Web The Master (Stm32H7) Is Supposed To Send Its Ack Bit But It Waits A Bit Longer Than The Previous Acks.

In this article, let’s discuss the i2c ack, nack, and i2c data validity. A serial clock pin (scl) that the arduino controller board pulses at a regular interval, and a serial data pin (sda). Addr (7 bits) i2c 7 bit address. So what does this nack imply?

I2C Configuration Must Be Written In The Sequence.

To read the state of a remote device's ack bit, the master must release sda before the. Data on the i2c bus is. Web technically the i2c address of bq27510 in 7 bit format is 0x55 so when you add the write/read bit then you get in 8 bit format 0xaa and 0xab respectively. Smbus block read¶ implemented by i2c_smbus_read_block_data() this command reads a block of up to 32 bytes from a.

Rd Equals 1, Wr Equals 0.

Web i ain't reading all that, also known as i ain't reading allat, is a tiktok sound originally said by tiktoker @thecubancrusher in december 2022 that's used in. Typical voltages used are +5 v or +3.3 v, although systems with other voltages are permitted. Web an i2c master, however, is free to change the state on sda any time it is asserting sck. Web reading and writing.

Web You Really Should Read The I2C Specification Here, But Briefly, There Are Two Different Cases To Consider For Ack/Nack:

A table showing several different. Go back to the vm operations list. We’ll use an example to show how to write to and read from adc using i2c. Without further ado, let us jump right into what is an i²c?